Building a custom SoC to run DOOM

This page will describe my experience building a custom RISC-V CPU for the sole purpose of running DOOM on a small FPGA (the Gowin Tang Nano 20K).

I will be creating a custom instruction set (RV32doom?) that augments the base RV32IM with instructions useful for running DOOM at full resolution and framerate on this FPGA.

I will also be implementing all of the Uncore components necessary for the CPU to function.

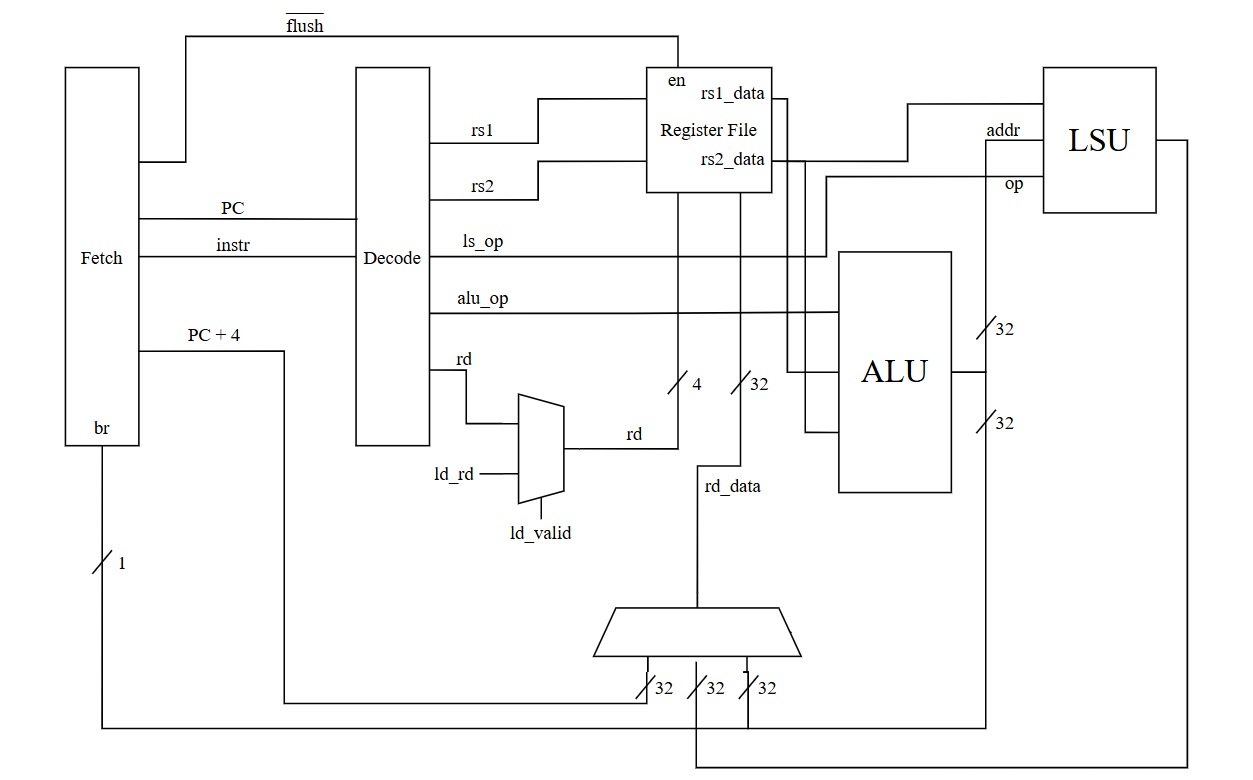

A very simplified diagram of the core pipeline

A very simplified diagram of the core pipeline