Decoding ADS-B on an FPGA

This project implements a complete, hardware-based ADS-B receiver pipeline by interfacing a HackRF One directly with a Gowin FPGA.

A demo of the working decoder receiving messages from a passing plane

A demo of the working decoder receiving messages from a passing plane

This project implements a complete, hardware-based ADS-B receiver pipeline by interfacing a HackRF One directly with a Gowin FPGA.

A demo of the working decoder receiving messages from a passing plane

A demo of the working decoder receiving messages from a passing plane

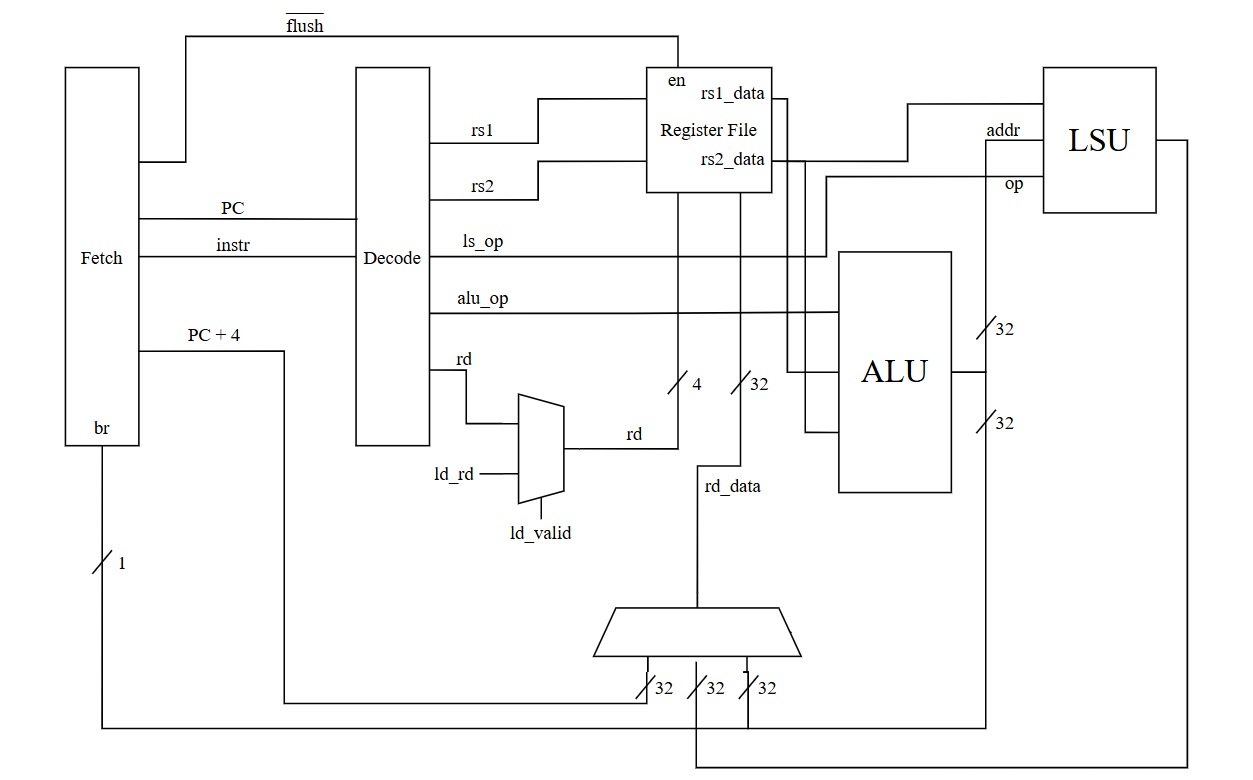

tiny-riscv is (true to its uninspired name) an attempt to build the smallest RISC-V core possible while maintaing roughly one Instruction per Cycle. It achieves this by supporting the base RV32E instruction set with a simple two stage pipeline. The implementation targets the FreePDK45nm standard cell library.

A very simplified diagram of the core pipeline

A very simplified diagram of the core pipeline